亲,“摩尔吧”已合并升级到更全、更大、更强的「新与非网」,提供电子产业图谱,星计划虚位以待。点击查看「新与非网」

课程简介

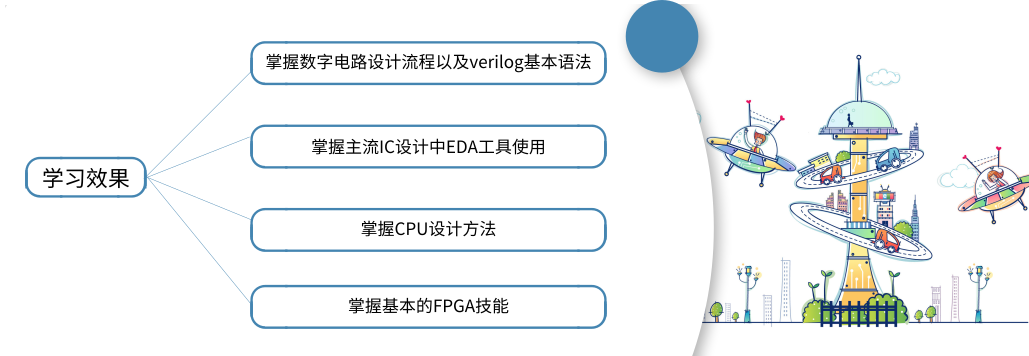

本系列课程从零开始,由浅到深介绍芯片设计流程常用 EDA 工具的使用、 Verilog 的语法基础,完整的软核处理器 verilgRTL设计,如何在自己设计的处理器上运行程序。

课程目录

数字芯片设计流程

1门课程 00小时27分钟

本章主要介绍ASIC流程和FPGA流程。

Verilog语法基础

1门课程 00小时44分钟

本章主要介绍verilog常用语法,使学员快速掌握一门硬件描述语言。

EDA工具使用

1门课程 00小时56分钟

本章主要介绍包括Design Compiler、Prime Time、Formality、VCS+verdi等,使想从事IC设计的学员掌握入门必备技能。

软核处理器设计

4门课程 02小时57分钟

本章以ARM架构为例,透过ARMv4 架构,详细讲解处理器的内部组成,该架构支持的指令集,在此基础上,从零开始,用verilog 一步一步实现处理器软核的设计。

处理器的仿真验证

1门课程 00小时45分钟

主要介绍如何在自己设计的处理器上运行程序,并移植到FPGA中实现。

学员评价

常见问题